IT之家 6 月 21 日新闻 ,据投资研究 平台 Tegus 披露的讨论内容,一位匿名英特尔总监表现,未来晶体管设计将低落对先辈光刻设备的依靠,转而提拔刻蚀技术的核心职位。他以为,随着全环绕栅极场效应晶体管(IT之家注:

|

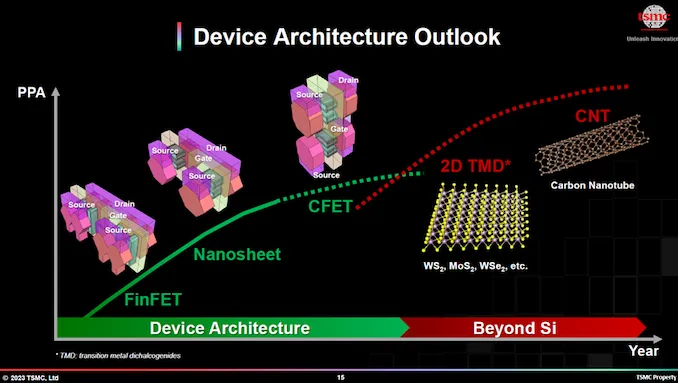

IT之家 6 月 21 日新闻 ,据投资研究 平台 Tegus 披露的讨论内容,一位匿名英特尔总监表现,未来晶体管设计将低落对先辈光刻设备的依靠,转而提拔刻蚀技术的核心职位。   他以为,随着全环绕栅极场效应晶体管(IT之家注:即 GAAFET)和互补场效应晶体管(CFET)等新型结构的发展 ,高端芯片制作 对光刻环节的总体需求将会削弱。  当前芯片制作 流程中:

这位英特尔总监强调,GAAFET 与 CFET 等三维晶体管结构哀求 “从各个标的目的 包裹栅极”,使得横向去除多余材料成为症结 ,“制作 商将更专注于经由过程 刻蚀工艺去除材料,而非延伸晶圆在光刻机中的处理 时间来缩小特征 尺寸。”

对于当前技术方案,目前最主流的还是鳍式场效应晶体管(FinFET),使晶体管底部连接绝缘材料,使电流经由过程 栅极来完成掌握 ;而新型设计则主要包罗: 英特尔总监表现,这种三维结构使芯片制作 “低落对最小特征 尺寸的依靠,因为不仅能在平面上实现高密度,还能经由过程 垂直堆叠告竣”,因此高数值孔径光刻机在先辈制程中的紧张性“将低于当前 EUV 设备在 7nm 及更先辈技术节点中的症结 职位”。 |

2025-05-03

2025-03-05

2025-02-26

2025-03-05

2025-02-26